|

|

|

|

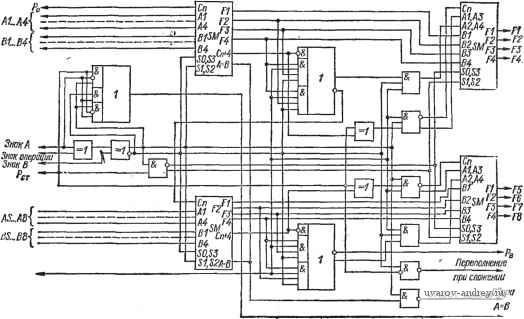

Главная страница » Электрика в театре » Схемы с частотным преобразованием 1 2 3 4 5 6 ... 16 м  ФС6ФС9 Г а R8 4=С? 2 iV?i iV2 Рис. 4. Схема датчика низковольтных сигналов величины и обеспечивает фильтрацию переменной составляющей частоты коммутирующего сигнала. Управление модулятором и демодулятором осуществляется генератором коммутирующего сигнала, построенным на двух транзисторах интегральной матрицы А2 и трансформаторе Т1, вырабатывающем переменное напряжение прямоугольной формы с частотой 30...40 кГц. Датчик предназначен для гальванического разделения цепей с потенциалом не более 1000 В и обеспечивает чувствительность не хуже 0,2 мкВ, приведенную погрешность - не более 1%, полосу пропускания - 0...2 кГц. В ячейке датчика предусмотрена регулировка коэффициента передачи в диапазоне 53,3... 133,3. Датчик напряжения предназначен для формирования и ввода в систему управления аналогового сигнала, пропорционального напряжению в различных цепях, с гальванической развязкой от последних. Датчик рассчитан на работу в цепях с напряжением до 1000 В отделителей напряжения, снижающих уровень преобразуемого напряжения до 10 В. Датчик напряжения построен аналогично датчику низковольтных сигналов, но в нем отсутствует видеоусилитель, т. е. сигнал проходит по тракту: модулятор - разделительный трансформатор - демодулятор - выходной усилитель. Датчик обеспечивает приведенную погрешность не хуже 1%, полосу пропускания - 0...1,3 кГц. В ячейке датчика предусмотрена регулировка коэффициента передачи в диапазоне 0,6... 1. Датчик модуля сигнала предназначен для преобразования знакопеременного входного сигнала постоянного тока в равный ему по модулю выходной сигнал определенной полярности. Ячейка также может использоваться в режиме сравнения двух однополярных сигналов с выделением большего по модулю. Принцип работы датчика вьщеления модуля заключается в том, что входной сигнал одной полярности не инвертируется за счет передачи двумя последовательно включенными инвертирующими операционными усилителя- щи С общим коэффициентом передачи, равным 1, а сигнал другой полярности инвертируется за счет передачи его одним усилителем с коэффициентом передачи, равным 1 (первый усилитель при этом отключается действием нелинейной обратной связи). Датчик обеспечивает приведенную погрешность преобразования не хуже 1 % при полосе пропускания 0...5 кГц. Датчик частоты вращения предназначен для формирования величины и полярности сигнала при использовании тахогенератора переменного тока. Датчик обеспечивает нормальную работу при изменении скорости в диапазоне 1 : 400 при погрешности не хуже 1 %. В группу задатчиков регулируемых параметров входят ячейки сельсинного и ступенчатого задатчиков, а также ячейка задатчика интенсивности. Ячейка сельсинного задатчика применяется с сельсин-ным командоаппаратом и предназначена для фазочувстви-тельного выпрямления выходного напряжения последнего с гальванической развязкой от линии связи. Ячейка обеспечивает возможность регулировки масштаба сигнала задания. Она имеет логическую схему, позволяющую осуществлять блокировки с контактными и бесконтактными путевыми выключателями с гальванической развязкой от их линий связи. Ячейка ступенчатого задатчика предназначена для ввода в САУ реверсивных сигналов задания, изменяющихся дискретно в функции положения коммутирующего устройства. Задатчик обеспечивает три ступени задания напряжения, раздельную регулировку их значения в диапазоне 0,01... .. .10 В, гальваническое разделение от линий связи коммутирующего устройства, ввод блокировок от путевых выключателей. Задатчик интенсивности предназначен для преобразования ступенчатых входных сигналов в линейно зависимое от времени напряжение для ввода в САУ. Задатчик интенсивности выполнен по схеме: релейный элемент с ограничением выходного сигнала - интегратор, охваченный общей от-рицательной обратной связью. Ячейка задатчика интенсивности обеспечивает регулировку времени развертки в диапазоне 0,5... 120 с. В группу гальванических разделителей входят разделители входных и выходных цепей. Гальванический разделитель входных цепей построен по типу датчика напряжения и отличается от него тем, что штепсельный разъем и изоляция трансформаторов рассчитаны на работу в диапазоне напряжений до 15 В. Гальванический разделитель выходных цепей предназначен для вывода сигналов САУ на регистрирующие приборы, исполнительные реле, элементы сигнализации и в другие САУ. В связи с этим он рассчитан на повышенную мощность выходного сигнала (20 В, 10 мА) при напряжении разделяемых цепей до 100 В. Разделитель выходных цепей построен по следующей схеме: входной усилитель - усилитель мощности - модулятор - разделительный трансформатор - демодулятор - фильтр. Управление модулятором и демодулятором осуществляется генератором коммутирующего напряжения, аналогичным примененному в датчике низковольтных сигналов. Приведенная погрешность преобразования обоих гальванических разделителей не хуже 1%. Компаратор предназначен для сравнения постоянных однополярных и двухполярных напряжений с предварительно установленным эталоном либо с изменяющимся во времени напряжением. Выходными напряжениями ячейки компаратора являются логические сигналы 1 (прямой выход) и О (инверсный выход). Для производства оперативных переключений в схемах в функции от контролируемых напряжений в ячейку встроены бесконтактные реле. Ячейка состоит из трех компараторов, построенных на операционных усилителях с положительной обратной связью, и узла логики. С помощью ячейки обеспечивается работа в двух режимах: 1) три независимых компаратора на один двухполярный или однополярный сигнал с прямым и ин- версным выходами каждый; 2) один трехвходовый компаратор двухполярных или однополярных сигналов с прямым и инверсным выходами. Входы в этом режиме собраны по схеме ИЛИ. В обоих режимах на входы компараторов могут подключаться бесконтактные реле и цепь задержки, обеспечивающая получение выходных сигналов с задержкой 3...7 мс. Компараторы обладают чувствительностью не хуже 50 мВ и предназначены для контроля напряжений в диапазоне 0,1...10 В. К элементам коммутации относится ячейка бесконтактных реле, которая предназначена для коммутации цепей в схемах с аналоговыми и дискретными сигналами. Ячейка состоит из 12 бесконтактных ключей со схемами управления. Пять бесконтактных ключей замыкаются при появлении на входах схем управления сигнала логической 1 , четыре - при появлении на входах сигнала логического О и три - в зависимости от установки тех или иных перемычек внутри ячейки при появлении на входах логической 1 могут замыкаться или размыкаться. Питание аналоговых элементов осуществляется децентрализованно от местных стабилизаторов напряжения, установленных в каждом блоке с аналоговыми элементами. Такая система принята для повышения помехоустойчивости САУ за счет развязки блоков по цепям питания, а также с целью дробления мощности стабилизаторов напряжения. Ячейка двухполярного стабилизатора ±15 В построена на базе микромодуля типа 701МП23 с транзисторными усилителями мощности на выходах. С помощью ячейки обеспечивается получение токов нагрузки по каждому каналу до 0,8 А при нестабильности выходного напряжения не хуже 0,05%. Каждый канал снабжен схемой защиты от короткого замыкания на выходе. Цифровые элементы серии УБСР-ДИ [24] построены на интегральных схемах серии К155 и имеют следующие уровни дискретных сигналов: 0...0,4 В - логический О , 2,4... .. .4,5 В - логическая 1 . Параметры сигналов цифроаналоговых преобразователей УБСР-ХШ, предназначенных для связи цифровых частей САУ с аналоговыми, унифицированы и согласованы с параметрами сигналов аналоговых элементов УБСР-АИ. Питание цифровых элементов осуществляется от стабилизированных источников напряжением 5 В, питание цифроаналоговых преобразователей - от стабилизированных источников ±15 В. Номенклатура серии цифровых элементов состоит из следующих групп: функциональные элементы (счетчики, сумматоры, регистры, арифметические устройства и др.), универсальные логические элементы, генераторы, элементы согласования, элементы ввода и вывода (шифраторы, индикаторы и др.), стабилизаторы напряжения, цифроаналоговые преобразователи. В ячейках серии УБСР-ДИ применены микросхемы малой степени интеграции, эквивалентные 10...90 дискретным радиокомпонентам (триоды, диоды и др.). В настоящее время промышленность освоила производство микросхем средней степени интеграции, имеющих на порядок больше радиокомпонентов. При использовании этих микросхем существенно снижаются габариты устройств, увеличивается их надежность и др. Основные типы микросхем средней степени интеграции следующие: К155ТМ7 - четыре D-триг-гера с прямыми и инверсными выходами; К155ИЕ6 и К155ИЕ7-двоично-десятичный и двоичный реверсивные четырехразрядные счетчики с возможностью преяварительной записи кодов; К155ИЕ8 - управляемый двоичным кодом делитель частоты; К155ИР13 - восьмиразрядный сдвиговый регистр; К155ИМЗ - четырехразрядный полный сумматор; К155ИГ13 - четырехразрядное арифметическое логическое устройство, которое выполняет 16 арифметических и 16 логических операций; К155ПР6 и К155ПР7 - преобразователи двоично-десятичного кода соответственно в двоичный и обратно; К155КП2 - селектор четырех каналов на один, на два разряда; К155ИДЗ - дешифратор на 16 вы- ходов; К155ИД1 - высоковольтный дешифратор для управления газоразрядными- индикаторами; К155ЛП5 - четыре двухвходовых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и др. На основе этих микросхем в НИИХЭМЗ разработаны дискретные элементы, предназначенные для построения цифроаналоговых и цифровых систем автоматического управления. Приведем краткую характеристику основных дискретных элементов. Универсальное арифметическое устройство АУ предназначено для суммирования или вычитания восьмиразрядных чисел с учетом их знака в двоичном или двоично-десятичном коде. Допускается соединение двух ячеек для получения шестнадцатиразрядного АУ. Результат операции получается в прямом коде. Кроме кода результата, устройство формирует знак результата, а также признаки переполнения при сложении и равенства чисел при их вычитании. Упрощенная схема АУ показана на рис. 5. Ее основой является микросхема К155ИПЗ. При подаче на ее управляющие входы Sq, Sg сигналов логическая единица (далее будем пи-еать 1 ), а на входы S, - логический нуль (будем писать О ) микросхема выполняет функцию полного четырехразрядного сумматора чисел А -ц В, поданных на ее информационные входы, а при инверсии этих сигналов код В заменяется на обратный код В. При вычитании двоичных чисел вычитаемое представляется обратным кодом и производится сложение кодов А-ц В. Если при этом образуется перенос из старшего разряда сумматора, то Л > 5, при этом нужно добавить единицу в младший разряд сумматора (что обычно делается по входу переноса), и результат получается в прямом коде. Если же перенос из старшего разряда сумматора отсутствует, то это значит, что Л < 5, и результат получается уже в обратном коде.  (Выбср кода) Рис. Б. Схема АУ Знакрелыпата в микросхеме К155ИПЗ вывод с„ является входом переноса для младшего разряда, а вывоДс +4 - выходом переноса из старшего разряда, причем перенос производится сигналами О . При оперировании с двоичными кодами на вход v подается сигнал О . На входы знак Л , знак 5 , знак операции подаются соответствующие сигналы, причем положительным числам и операции суммирования соответствует О . На вход Рст подается выход переноса из старшего разряда устройства, т. е. выход Pg данной схемы, если используется только одна ячейка АУ, или выход Pg ячейки, соответствующей старшим восьми разрядам, если используются две такие ячейки. Узел определения знака представляет собой комбинационную схему, на выходе которой формируется сигнал знака результата, а также сигнал, задающий режим работы микросхемы К155ИПЗ - с прямым или обратным кодом числа В. Вторая пара микросхем в режиме вычитания при отсутствии переноса кз старшего разряда инвертирует код выхода первой пары. В режиме двоично-десятичного суммирования на вход V подается 1 . Рассмотрим кратко правила арифметических операций в двоично-десятичном коде 1-2- 4-8. При сложении таких чисел перенос из младшей тетрады результата в старшую (тетрадой называется четыре двоичных разряда, кодирующих одну десятичную цифру) происходит, если результат суммирования тетрад А к В больше 9, о чем свидетельствуют наличие либо переноса из старшего разряда тетрады (результат больше 15), либо единицы во втором и четвертом разрядах (результат равен 10 или И), либо единицы в третьем и четвертом разрядах (результат равен 12, 13, 14, 15). Если переноса из данной тетрады нет, то результат окончательный. Если же перенос имеется, : то результат необходимо скорректировать, т. е. от суммы отнять 10, что равносильно прибавлению к сумме кода Olio с отбрасыванием переноса, который может получиться при корректирующем сложении. В режиме вычитания двоичные разряды вычитаемого заменяются обратными величинами, после чего производится суммирование по правилам двоичной арифметики, т. е. перенос из тетрады в тетраду происходит, если сумма более 15. Далее, если при этом сформировался сигнал переноса из старшей тетрады, то Л > 5 и нужно добавить число 10 (код 1010) к тем тетрадам суммы, из которых не было переноса. Если же переноса из старшей тетрады нет, то А <С В и необходимо взять обратный код двоичных цифр суммы и прибавить 1010 к тем тетрадам, откуда был перенос, причем переносы между тетрадами игнорируются. В схеме АУ описанный алгоритм для каждой тетрады реализуется с помощью схемы ИЛИ - И с прямыми и инверсными выходами, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и двух схем И. При построении цифровых и цифроаналоговых САУ ячейка АУ используется как цифровое сравнивающее устройство (рис. 2, б), а также в некоторых случаях в цепях задания для формирования кода эталонной (входной) величины. Ячейки двоичного (РС-3) и двоично-десятичного (РС-4) реверсивных счетчиков предназначены для подсчета поступивших на их вход числа импульсов с выдачей результата соответственно в двоичном 12-разрядном коде или двоично-десятичном трехтетрадном коде 1-2-4-8. Основой этих ячеек являются микросхемы К155ИЕ7 и К155ИЕ6. Упрощенная схема ячейки РС-4 изображена на рис. 6. Схема ячейки РС-3 отличается только соединением цепей защит от переполнения. Счетные импульсы подаются на входы -Ь или - в зависимости от направления счета. Входы 4 и 2 соединяются с выходами О и 999 соответственно. На входах !/ и 5 должны быть сигналы О . Если на одном из этих входов 1 , то импульсы данного направления счета на счет- 1 2 3 4 5 6 ... 16 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |