|

|

|

|

Главная страница » Электрика в театре » Мультиплексоры демультиплексоры в последовательностных схемах 1 2 3 4 5 6 7 8 ... 39 выбирается ао и как следствие [/] =0. Для

выбирается ci, в результате чего = Для

выбирается аг, при этом [f] = l. Для

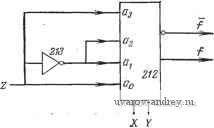

выбирается аз, и в результате [f] =0. Рассмотрим асимметричную цепь с картой Карно, приведенной на рис. 2.4. Функция f(X.r,Z) = 2(l,2,4,7) может быть представлена в виде логического произведения как [01101001] = [f]- Как и в случае реализации на мультиплексоре функции ИСКЛЮЧАЮЩЕЕ ИЛИ, данное решение тривиально, посколь- 00 Of П 10 Рис. 2.4. iC-карта для симметричной функции. ку на все входные линии подаются постоянные значения переменных О или 1. При этом возможности мультиплексора используются незначительно. Более эффективное решение может быть получено при устранении одной из переменных (соответственно и из матрицы селектирования). Это можно сделать, используя следующие правила из гл. 1: 0+0 = 0, 0-f Z=Z, 0 + Z = Z, Z-fZ = I. Выходная функция, соответствующая рис. 2.4, может быть разложена по минитермам в следующем виде: / = XYZ-\-XYZ -\-XYZ-XYZ. Переписывая эту функцию в виде ;=ZXY-lrZXY + ZXY-JZXY и интерпретируя Z и У как компоненты селекторной переменной, а Z как входную переменную, получаем ao=Z, ai=Z, a2=Z и аз=2. В соответствии с этим / может быть представлена с ис- Рис. 2.5. Логическая схема для симметричной функции на мультиплексоре 4X1.  пользованием операции логического умножения матриц в виде [Z Z Z Z] Логическая схема, реализующая данную функцию на основе указанного уравнения с использованием мультиплексора, представлена на рис. 2.5. 2.4. ПРЯМОЙ МЕТОД ПРОЕКТИРОВАНИЯ СХЕМ НА МУЛЬТИПЛЕКСОРАХ В качестве примера рассмотрим выходную функцию f{A, В, С), соответствующую карте Карно на рис. 2.6. В этом случае матрицу значений входных переменных получим непосредственным

анализом карты Карно, а не путем разложения функции по минитермам с последующим преобразованием. В качестве селекторных выберем переменные Л и В. Анализируя столбец карты. для которого [ЛБГ=[ООР, обнаруживаем, что значение функции равно О для обеих клеток столбца (обоих значений С), т. е. ао=0. Для столбца с [Л В] = [0 IF функция на выходе равна 1 при С=1, т. е. ai = C. Для [Л B]t={\ QY функция f также равна 1 при С=1, т. е. С2=С. Для [Л ВГ = [1 1Г значение функции f равно 1 для обоих значений С, а аз=1. Соответствующая схема мультиплексора 4x1 изображена на рис. 2.7. ° т л в

Рис. 2.7. Логическая схема переноса Рис. 2.8. Карта Карно для компара- разряда, выполняемая на мультиплек- тора. Мультиплексоры с четырьмя входными линиями обычно изготавливают по два на одном кристалле. При этом селекторные линии к ним являются общими. Такое конструктивное решение оказывается очень удобным при логическом проектировании. Восьмивходовые мультиплексоры находят широкое применение, так как компактно размещаются на одном кристалле. Их можно использовать для схем с четырьмя или большим числом входных переменных. В качестве примера рассмотрим схему компаратора, карта которого приведена на рис. 2.8. На этой карте представлены значения выходной функции /ь причем /i = 1 в тех Символ t используется в качестве знака транспонирования. В частно- сти, [А В]=[0 0] следует понимать, как

. - Прим. перев. случаях, когда три или большее число входных переменных принимают значения 1. Если из четырех исходных переменных три (Л, В, С) являются селекторными, то каждой входной линии мультиплексора должны соответствовать значения в двух клетках карты Карно. Из этих пар клеток по существу получается карта Карно для оставшейся переменной D. Для значение функции fi равно О как при £ = 0, так и при D = 0. Следовательно, ао=0. То же справедливо и для [Л В С]=[0 О 1] [О 1 0] и [1 О OF, а поэтому ai=a2 = G4=0. Однако для [Л В CF=[0 1 IF. [1 О IF и [1 1 OF при D=0 значение равно О, а при D=\ значение равно 1; следовательно, 03=05 = сб=£). При [Л В СУ=[\ 1 IF значение fi равно 1 как при D=\, так и при D=\, а поэтому 07 = 1. На рис. 2.9 показана реализация этой схемы на восьми-входовом мультиплексоре. Рис. 2.9. Реализация компаратора на мультиплексоре. /\ в с' в данной книге часто используется прием одновременного изображения нескольких выходных функций на одной карте Карно или одним уравнением с логическим умножением. Чтобы продемонстрировать возможности работы с несколькими выходами, видоизменим логику функционирования предыдущей схемы, так чтобы она удовлетворяла требованиям дешифратора с принятием решения голосованием . Предположим, что четверо судей по отдельности выносят решения о результатах некоторого соревнования. Если не менее трех судей выносят решение да , то и общее решение, несомненно, должно быть да . Если двое судей говорят да , а двое - нет , соревнование должно

Рис. 2.10. Карта Карно для дешифратора с принятием решения голосованием>.

быть проведено повторно. Если лишь один из судей говорит да или никто не высказывает такого мнения, то общим результатом должно быть нет , /(-карта для такой схемы изображена на рис. 2.10. Значениями fi = l отмечены клетки, для которых единице равны не менее трех переменных из ABCD. Значениями /2=1 отмечены клетки, для которых равн.! 1 не менее двух переменных. Таким образом, ДА=/1, НЕТ=/2, ПОВТОРЕНИЕ (неопределенность) =f2-/i. С использованием символики логического умножения для такой схемы получаем уравнение О О О D О D D 1 О D D 1 D 1 1 1 Следует обратить внимание на форму этого уравнения. Выходная матрица определяет количество переменных в выходной функции и присваивает имя каждой переменной. Каждой переменной на выходе соответствует строка во входной матрице. Матрица селектирования определяет селекторные переменные и порядок, Б котором они используются при выборе столбца входной матрицы. Если уменьшить количество селекторных переменных с 3 до 2, то дешифратор с принятием решения голосованием можно реализовать на сдвоенных четырехвходовых мультиплексорах. Если две {А, В) из четырех исходных переменных используются в качестве селекторных, то каждой входной линии мультиплексора соответствуют четыре клетки карты. Эти четыре клетки определяют соответствующие /С-карты для двух остальных переменных CD. Для функции fi значения селекторных переменных АВ определяют четыре столбца карты, изображенной на рис. 2.8. Селекторная переменная АВ принимает следующие значения: а) ЛВ=00, б) ЛВ = 01, в) ЛВ=10, г) АВ = П. Соответствующие карты для CD приведены на рис. 2.11, а - г. Для функции fi карты переменных CD даны на рис. 2.12.

Рис. 2.11. Карты Карно для U и входных переменных С и D. а -при .4В=00, ао=0; 6 - при ЛВ=01, a,=CD; в - при ЛВ=10, a!=CD; г - при Лй=11. аз=С+0. При Проектировании таких схем целесообразно отыскивать одинаковые входы или входы, отличающиеся друг от друга инверсией. Схема дешифратора с принятием решения голосованием на мультиплексорах 4X1 представлена на рис. 2.13. Для полноты на этом же рисунке изображены и другие функции, реализуемые на мультиплексорах 2x1.

а Рис. 2.12. Карты Карно для fi и входных переменных С и D. с -при ЛВ=О0, ao=CD; б -при АВ=01, a,=C+D; в - при ЛВ=10, Cs=C+D; г -при ЛВ=11, Сз=1. В настоящее время уже выпускаются мультиплексоры с 16 входами, на которых можно создавать схемы с числом входных переменных пять и более. Учитывая физические размеры этих мультиплексоров и возникающие при их использовании трудности в процессе проектирования, видимо, целесообразнее пользоваться мультиплексорами с числом входов не более восьми.

о, а, 2П НЕТ ПОВТОРЕНИЕ Рис. 2.13. Логическая схема дешифратора с принятием решения голосованием на двойном мультиплексоре 4X1 и мультиплексорах 2X1. Мультиплексоры оказываются весьма удобными конструктивными элементами при создании комбинационных схем. Основными достоинствами их использования являются следующие: а) сокращение числа соединений и объема пайки, б) уменьшение стоимости элементов и монтажа. Недостатками можно считать: а) как правило, повышенное потребление энергии, б) трудности перестройки схем на печатных платах. 2.5. ЭТАПЫ ПРОЕКТИРОВАНИЯ СХЕМ НА МУЛЬТИПЛЕКСОРАХ Проектирование схем на мультиплексорах включает следующие этапы: 1) определение входных и выходных переменных; 2) запись матричного уравнения, содержащего матрицу входных переменных, вектор селекторных переменных и вектор выходных переменных; 3) изображение логической схемы на мультиплексорах, реализующей требуемые функции. 2.6. ИСПОЛЬЗОВАНИЕ ЗАПОМИНАЮЩИХ УСТРОЙСТВ (ЗУ) НА БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМАХ (БИС) В КАЧЕСТВЕ ЭЛЕМЕНТОВ КОМБИНАЦИОННЫХ СХЕМ Если вернуться к вопросам, излагавшимся несколько раньше, то можно обнаружить одно интересное конструктивное решение. Запишем функцию в виде произведения матриц [А] [Z] = [/] и рассмотрим описанный ранее как тривиальный способ ее реализации, когда элементами [А\ являются только нули и единицы. Уже отмечалось, что умножение матриц можно рассматривать как операцию адресации. В то же время выполняемые на больших интегральных схемах (БИС) запоминающие устройства (ЗУ) с произвольным доступом и постоянные ЗУ хранят информацию именно в виде нулей и единиц и имеют адресные Сигнал . разрешения ZZ5\ 1>-1 Y Y ZZii Рис. 2.14. Типовая логическая схема демультиплексора. шины для доступа к ней. Поэтому при соответствующем подборе матрицы [Л] и использовании матрицы [Z] как адреса элемента памяти можно получать комбинационные схемы на БИС памяти. Такое решение наиболее эффективно, когда требуется большое число функций на выходе или необходимо многократное дублирование одной и той же схемы. Достоинством проектирования схем на БИС являются возможность минимизации межэлементных связей и большая плотность размещения элементов. 2.7. ДЕМУЛЫИПЛЕКСОРЫ Логическая схема демультиплексора изображена на рис. 2.14. Демультиплексор является стандартным конструктивным элементом, выполняющим функции, противоположные функциям мультиплексора. У демультиплексора один вход и много выходов. Таблица 2.1 Соответствие входных и выходных значений для демультиплексора

Входную линию демультиплексора можно рассматривать как источник сигнала разрешения. Схема демультиплексора отличается от схемы мультиплексора тем, что у нее нет вентиля на выходе. Из-за отсутствия этого вентиля функции на выходе обычно имеют инвертированные значения. При нулевом входном сигнале единице равны значения всех выходных переменных, кроме селектируемой, равной нулю. Демультиплексоры используются в комбинационных схемах с большим числом выходных функций. Проектировать схемы на основе демультиплексоров удобнее всего с помощью карт Карно. о 1 Рис. 2.15. Карта Карно для демультиплексора. Когда на вход мультиплексора, изображенного на рис. 2.14, поступает сигнал, равный 1 для всех значений XY, Когда же входной сигнал (сигнал разрешения) равен О, связь между значениями сигналов на селекторных и выходных линиях может быть представлена в виде табл. 2.1 или карты Карно (рис. 2.15). Для селекторных переменных в клетках карты указаны соответствующие функции {fi, fz и т. д.), а не их значения. Сигнал разрешения Демульти -пленсор Рис. 2.16. Блок-схема демультиплексора. Выз;оды Селекторные линии На карте Карно не отражена необходимость инвертирования сигналов, о чем нужно помнить при построении реальных схем. Демультиплексоры изображают на логических схемах так, как показано на рис. 2.16. Инвертирование выходных сигналов обозначено маленькими кружками. 2.8. УПРАЖНЕНИЯ У.2.1. Спроектируйте схемы, реализующие приводимые ниже функции, используя мультиплексоры с числом селекторных линий, на единицу меньшим количества входных переменных. а) f=BcD + BCD; б) f=lBC+BCD; в) f=AC+BC; г) f=BC+AC; д) f==BCD+AC- е) f=B+C; ж) f=AB+AC+AD. У.2.2. Используя мультиплексоры 4X1 и 2X1, спроектируйте схемы, соответствующие следующим функциям: а) f{A, В, С, £)=S(0, 1, 7, 8, 9, 10, 14, 15); б) f( W, X, Y, Z)=S(0, 1, 2, 3, 4, 5, 10, 11, 12, 13); в) f( а, b, с, d)=S(l, 2, 4, 7, 8, 11, 13, 14); г) f(r, s, t, ы)=2(0. 2, 3, 5, 10, 11, 12, 13). У.2.3. Разработайте на мультиплексорах 4X1 схему, на выходе которой значения функции f-x+ix определяются для значений х от О до 7. У.2.4. Разработайте на мультиплексорах схему, выполняющую полное суммирование или полное вычитание. У.2.5. Коды, обеспечивающие проверку на четность, помимо информационных имеют один дополнительный разряд, который помогает обнаруживать ошибку в отдельном байте или слове. Хемминг показал, что включение трех Дополнительных разрядов позволяет не только обнаружить сам факт одиночной ошибки, но и исправить ее. -Подобный код, предназначенный для обнаружения и исправления ошибок, носит название кода Хемминга. В табл. У.2.1 показан переход от двоично-десятичного представления числа 1 2 3 4 5 6 7 8 ... 39 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |