|

|

|

|

Главная страница » Электрика в театре » Мультиплексоры демультиплексоры в последовательностных схемах 1 ... 28 29 30 31 32 33 34 ... 39 ЧТО заставляет передатчик сформировать символ прерывания передачи. Единичное значение бита D2 разрешает передачу сигнала через вывод RxE, что в свою очередь разрешает выдачу сигнала управления приемом RxR. Бит Dl = l обеспечивает низ-кий уровень сигнала управления модемом на выходе DTR. Бит D0=1 разрешает выдачу сигнала через вывод TxEN, что выводит линию TxD буфера передатчика из состояния ожидания. Приводимый ниже фрагмент программы для USART обеспечивает выдачу сигнала RTS, выполнение проверки передаваемых данных на четность, использование одного стопового бита при длине передаваемого символа 8 бит и отношении частоты тактовых импульсов к скорости передачи 16. MVI А,40Н D6=l OUT USART Сброс USART MVI A,7EH Задание количества стоповых бит, про- верка данных на четность/нечетность и т. п. OUT , USART Загрузка в USART управляющего слова MODE INSTRUCTION MVI А,27Н Задание управляющих сигналов RTS, Т, R и DTR OUT USART Загрузка в USART управляющего слова COMMAND INSTRUCTION Команда MVI пересылает данные в регистр А. Шестнадцатеричное число 40=010000002, задающее единичное значение биту D6, обеспечивает сброс устройства и переводит его из состояния управления передачей данных в состояние задания режимов работы. Команда иллюстрирует использование средств сброса устройства. Шестнадцатеричное число 7Е определяет количество стоповых импульсов, тип проверки на четность/нечетность, длину символа и скорость передачи. Если задается режим работы USART, то установка сигналов RTS и разрешения приема (RxE) осуществляется выбором шест-надцатеричного числа 27 в качестве значения управляющего> слова COMMAND INSTRUCTION. Команды OUT направляют данные к соответствующему адресату. Синхронный режим. USART может также работать в синхронном режиме передачи данных. В этом случае в регистр управления пары регистров управления/состояния загружаются. четыре управляющих слова. Первые три управляющих слова должны загружаться в определенной последовательности посла-сброса устройства согласно рис. 7.13. Последнее управляющее СЛОВО COMMAND INSTRUCTION может загружаться и изменяться после этого в любой момент времени путем подачи управляющего сигнала C/D=l. Управляющее слово I (CW1) задает режим работы устройства, управляющие слова 2 и 3 (CW2 и CW3) являются синхронизирующими символами. Управляющее слово 4 (CW4) управляет передачей данных. Формат этого управляющего слова приведен в табл. К.5 приложения К. Формат управляющего слова MODE INSTRUCTION при работе в синхронном режиме в основном соответствует тому, который демонстрирует табл. К.4, за исключением битов, приведенных в табл. К-б.

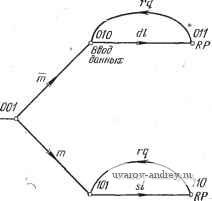

ТхЕ Рис. 12.10. Автоматическое включение синхронизирующих символов. При работе в синхронном режиме биты D1 D0=00 управляющего слова MODE INSTRUCTION задают синхронный режим передачи данных. Если указан этот режим, то бит D7 определяет количество синхронизирующих импульсов. Если D7=l, то используются одиночные синхронизирующие импульсы, если же D7=0 - сдвоенные. На рис. 12.10 показано включение синхронизирующих импульсов в выходной поток данных передатчика, выполняемое интерфейсом автоматически. Вывод, используемый для управляющего сигнала SYNDET (обнаружение синхросигнала), показан на рис. 12.9 в группе выводов сигналов управления приемом. При вводе используется сигнал SYNDET, поступающий извне, и символы данных считываются при поступлении следующего сигнала RxC. Сигнал SYNDET указывает появление последней группы синхроимпульсов при выполнении приема данных. Сигнал SYNDET сбрасывается при чтении ЦПУ информации о состоянии USART. Бит D6 задает источник синхронизации. Если D6=l, используется внешняя синхронизация, если D6=l-внутренняя. Назначение бит D5, D4, D3 и D2 со- ответствует описанию формата управляющего слова для асинхронного режима передачи (см. табл. К.4 приложения К). Формат содержимого регистра состояния. ЦПУ может в любой момент времени определить состояние USART, прочитав содержимое регистра состояния пары регистров управления/со- стояния. Формат содержимого этого регистра показан в табл. К.7 приложения К- Доступ к регистру осуществляется генерацией в USART сигнала RD при C/D=l. Бит D7 используется для определения наличия сигнала DSR, бит D6 - синхронизирующего символа (сигнала на выводе SYNDET). Последнее приводит к автоматическому сбросу синхронизирующего сигнала. Бит D5 указывает на ошибку в формате посылки, бит D4 - на потерю символа, бит D3 - на обнаружение ошибки при проверке на четность/нечетность. Бит D2 является признаком состояния вывода выходного сигнала управления передачей ТхЕ; бит D1-признаком состояния вывода выходного сигнала управления приемом RxR, а бит DO - признаком состояния вывода сигнала передатчик готов TxR. Щ 12.3. УПРАЖНЕНИЯ У.12.1. Световой индикатор с 7-сегментным дешифратором знаков описан в. упражнении У. 1.6. Составьте подпрограмму вывода повторяющейся последовательности чисел от О до 4, отображаемых указанными семью сегментами. Используйте стандартный интерфейс ввода-вывода. Обеспечьте задержку вывода каждой последовательности чисел приблизительно на 5 с. У.12.2. Упрощенный граф переходов устройства ввода, отражающий как ввод информации о состоянии, так и самих данных, показан на рис. У.12.1. На рис. У.12.2 приведена схема алгоритма пуска и работы устройства, проверки его состояния и ввода данных.  Ввод информации о состоянии О

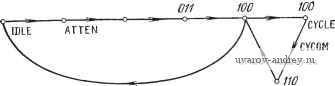

Регистр управления Рис. У.12.1. Граф переходов схемы ввода данных и информации о состоянии. На графе переходов (рис. У.12.1) использованы следзтощие сокращенные обозначения: а) для вводимой информации: rq--запрос на ввод, si - вводимые признаки состояния, dl - вводимые данные; б) для выводимой информации: RP - ответ на запрос, Л1(т)-бит 3 (бит задания режима работы), R - бит 6 (бит сброса устройства, т. е. перевода в состояние ожидания). У.12.3. Граф переходов на рис. У.12.3 представляет собой модификацию графа на рис. 6.16 и показывает только сигналы управления адаптером вво- ЛВмшнение ( директив VNAMEORG Запретить прерывания, адресуеные указателем стека sp Инициировать работу адаптера интерфейса Загрузить упраВляюиие сигналы в регистр адаптера: витЗ=М, Sum 6=0 Установить счетчик числа передач байтов данных Ожидать ответа (сигнала RP) Уменьшить содержимое счетчико но 1  Запросить загрузку Ванных Нет Установить бит В=1 Рис. У.12.2. Схема алгоритма работы интерфейса передачи данных и информации о состоянии. ООО 001 GO 010  Рис. У. 12.3. Граф переходов обобщенного интерфейса для микро-ЭВМ. да-вывода. Составьте подпрограмму, выполняющую следующие операции: а) инициирование выдачи двух выходных управляющих сигналов GO и CYCOM и ввод двух управляющих сигналов CYCLE и IDLE для двух портов А и В; б) управление портом Айв случае, когда биты второго, третьего и четвертого разрядов этого порта равны 1 (сигнал ATTENTION), выдача сигнала GO; в) чтение информации из порта В при поступлении сигнала CYCLE и выдача сигнала CYCOM; г) переход к шагу б при поступлении сигнала IDLE. У.12.4. Программа для связного интерфейса должна обеспечить передачу сообщения HAVE А GOOD DAY . Обеспечьте проверку передаваемых данных на нечетность, максимальное количество стоповых битов и минимальную скорость передачи данных. У.12.5. Напишите программу, обеспечивающую проверку связного интерфейса на ошибки в формате посылок и потерю символов. ГЛАВА 13 КОМПОНОВКА И ПУСК МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ Базовый набор машинных команд микропроцессора приведен в гл. 11. Глава продолжается описанием техники разработки программ, основанной на использовании ОЗУ для имитации работы ПЗУ, и методов выполнения программ, находящихся в ОЗУ. Такое использование ОЗУ преследует цель создания виртуальной машины, имитирующей в ОЗУ работу ПЗУ. Эту систему удобно применять в качестве обучающей для ознакомления начинающего программиста с набором команд. При этом облегчается работа программиста. Проверку и модификацию программы легче проводить при ее размещении в ОЗУ, поскольку в этом случае корректировку текста программ и устранение ошибок можно выполнять с консоли микро-ЭВМ. Однако структура системы, предназначенная для разработки программ, плохо согласуется с требованиями к системе, ориентированной на обработку данных, по следующим причинам: 1. ОЗУ является не очень подходящей средой для размещения программ из-за его дороговизны, громоздкости и плохой надежности. 2. Система, предназначенная для разработки программ, использует разнообразные средства ввода-вывода, такие, как дисплей, которые могут и не требоваться в процессе обработки данных. Более подходящим может оказаться использование светового табло или других компактных устройств ввода-вывода, предназначенных для связи человека с микро-ЭВМ. 3. Универсальность не требуется, поскольку задачи разработки программ и обработки данных являются различными. 4. При разработке программ пользователя требуется большое число обслуживающих программ (трансляторов ассемблера, редакторов текста и т. д.), которые не нужны во время обработки данных. Вследствие этого может отпасть необходимость в использовании таких компонент, как накопители на гибких магнитных дисках. Целью данной главы является описание начальных этапов проектирования микропроцессорной системы, предназначенной для обработки данных. Этими этапами являются: 1) выбор системы адресации; 2) выбор и взаимное соединение отдельных элементов; 3) создание средств начального пуска системы (инициализация программы). Перечисленные этапы подробно описываются в следующих разделах [31, 32]. 13.1. СИСТЕМА АДРЕСАЦИИ Выбор системы адресации заключается в присваивании уникальных адресов каждому байту ОЗУ, ПЗУ и каждому порту ввода-вывода. Эта процедура имеет важное значение, посколы<у в разных микропроцессорных системах реализуются различные способы оптимизации доступа к ОЗУ и портам ввода-вывода. Выбором определенной системы адресации можно обеспечить эту оптимизацию. В следующих разделах приводятся рекомендуемые схемы адресации системы. □ 13.1.1. Адресация в микро-ЭВМ фирмы Motorola Типичная карта адресного пространства для микро-ЭВМ фирмы Motorola показана на рис. 13.1. Здесь отдается предпочтение рещению проблемы адресации памяти. Прямая адресация требует присваивания ОЗУ первых 256 адресов (с 0-го по 255-й) В гл. II показано, что это сокращает время выполнения команд обращения к памяти. Шестнадцатери чный адрес FFFF FFF8 8FFF 8W0 Ш1 ОПГ Специальное ПЗЬ Не использрется Не используется Память еВода-ВыВода Не используется ОЗУ Рис. 13.1. Типичная схема адресации памяти микропроцессоров фирмы Motorola.

Чтобы продемонстрировать эффект не использования двоичных разрядов А13 и А12 адреса, рассмотрим 4-разрядный шестнадцатеричный адрес. .Возможность обращения к одному Принципы функционирования микропроцессорных систем фирмы Motprola требуют, чтобы ячейки памяти со старшими адресами резервировались для размещения команд начального пуска (инициализации работы ЦПУ) и обработки прерываний. Поэтому старшие адреса присваиваются ПЗУ. В микропроцессорных системах фирмы Motorola устройства ввода-вывода рассматриваются как память с большим временем обращения. На схеме системы адресации адреса портов ввода-вывода размещены где-то посередине между адресами ОЗУ к ПЗУ. Связь между ПЗУ и ОЗУ демонстрирует рис. 10.14. Существует несколько рекомендаций по эффективной организации адресного пространства микропроцессорной системы^, из которых особого внимания заслуживают следующие: 1) закрепление части адресов за портами ввода-вывода; 2) введение избыточности ( пустот ) в карту адресного пространства. Выбор конкретных адресов портов ввода-вывода всегда является проблемой. Издержки процесса проектирования можно значительно сократить, если при переходе от разработки одной системы к другой присваивать одни и те же адреса портам ввода-вывода. При этом предполагается, конечно, тщательный выбор адресов для первой проектируемой системы. Схема адресного пространства на рис. 13.1 содержит пустоты . Из 65 536 возможных адресов ячеек памяти 1024 предназначены для ПЗУ, 16 - для портов ввода-вывода и 384 - для1 ОЗУ, т. е. всего использовано 1424 адреса. При работе с такой схемой адресации нет необходимости в использовании всех линий адресной шины. Для иллюстрации этого утверждения рассмотрим первые четыре двоичных разрада адреса (т. е. разряды. А15, А14, А13 и А12). Поскольку карта адресного пространства имеет пустоты , то разряды А13 и А12 не используются. Выходы ПЗУ, блоков PIA и блоков ОЗУ подключаются к адресной шине следующим образом: И тому же адресату адресного пространства с пустотами показывают следующие числа: Шестнадцате- Ячейки карты ричный адрес адресного пространства 1ХХХ Тот же самый байт ОЗУ 2ХХХ 4ХХХ 5ХХХ Тот же самый регистр устройства ввода-вывода * 6ХХХ 7ХХХ 8ХХХ 9ХХХ АХХХ ВХХХ Тот же самый байт ПЗУ DXXX FXXX Таким способом можно значительно сократить количество линий адресной шины. □ Д| 13.1.2. Система адресации микро-ЭВМ фирмы Intel Типичная карта адресного пространства микро-ЭВМ фирмы Intel показана на рис. 13.2. Здесь предпочтение отдается решению задач инициализации работы программы и организации ввода-вывода. Для начального пуска системы зарезервированы первые 64 ячейки памяти, используемые при выполнении функций рестарта. Однако первые 256 (FFie) ячеек памяти, предоставляемые изолированным устройствам ввода-вывода, имеют двойное назначение. Один и тот же адрес (например, TFie) относится как к памяти, так и к устройству ввода-вывода. С целью повышения скорости передачи данных в микропроцессорах фирмы Intel команды обращения к памяти и команды ввода-вывода обрабатываются по-разному. Отличие состоит в том, что содержимое изолированных устройств ввода-вывода может передаваться только в аккумулятор, тогда как передача содержимого памяти может осуществляться с помощью всего набора команд пересылки данных. Ввод-вывод может быть включен и непосредственно в систему адресации микро-ЭВМ. В этом случае к устройствам ввода-вывода (УВВ) можно обращаться, задавая адреса так же, как и при обращении к памяти. Представление портов ввода-вывода как обычным образом адресуемых ячеек памяти имеет то преимущество, что для управления этими портами может быть ис- Щестнадцатерачныи адрес FFFF F80F F800 WOO D3FF 003F 0000 Не используется Область,зарезерВироВан нал для бвода-ВыВода Не используется ОЗУ Не используется ПЗУ Специальное ПЗУ ИзолироВанно/е УВВ Рис. 13.2. Типичная схема адресации памяти микропроцессоров фирмы. Intel. пользован мощный набор команд. Недостаток такого решения в том, что выполнение команд обращения к памяти занимает большее количество машинных циклов, чем специальные команды ввода-вывода. На рис. 13.3 показан обычно используемый способ выборки ОЗУ, ПЗУ и портов ввода-вывода, адресуемых как ячейки памяти (рис. 13.2), с помощью демультиплексора и двух линий адресной шины А15 и А14. Для данной карты адресного пространства с пустотами линии адресной шины А13, А12, АН и А10 игнорируются. По мере того как все большая часть адресного пространства системы будет заполняться, не участвующие 1 ... 28 29 30 31 32 33 34 ... 39 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |