|

|

|

|

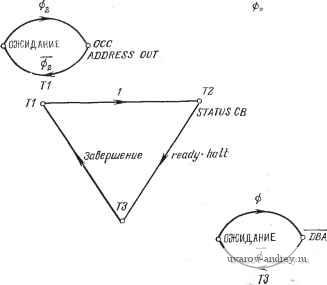

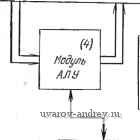

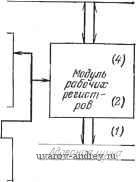

Главная страница » Электрика в театре » Мультиплексоры демультиплексоры в последовательностных схемах 1 ... 19 20 21 22 23 24 25 ... 39 держимое регистра загружается в аккумулятор и на АЛУ подается команда сложения. Кроме того, на линию ЧТЕНИЕ/ЗАПИСЬ подается сигнал низкого уровня, т. е. линия переводится в состояние, соответствующее записи. В этом состоянии выполняется последнее действие по обслуживанию. Если установлен сигнал НА, то схема переходит в режим ожидания. Если этот сигнал не подан и поступает запрос на прерывание, то в еди-ашчное состояние устанавливается триггер прерывания (INT FF) 5/7 0OI Шит данных Буфер даннысс \  Управляющий модуль Адресная шина Шина упра£ления s Рис. 10.8. Структурная схема, иллюстрирующая выполнение машинного цикла 1 для случая сложения содержимого регистра и содержимого аккумулятора. и вырабатывается выходной сигнал подтверждения прерывания. Если состояние Т4 является последним, а в данном случае это так, и триггер НА не установлен, то при поступлении очередного синхроимпульса Ф\ происходит переход в состояние Т1. Выполнение описанного машинного цикла можно также проследить по структурной схеме, представленной на рис. 10.8. По первому синхросигналу (1) адрес подлежащей выполнению команды посылается из модуля рабочих регистров на адресную шину и в то же время управляющий модуль получает информацию о состоянии микропроцессора. Характерным содержанием такой информации является сообщение о необходимости прерывания или останова. Что касается описываемого машинного адикла, то принимаемая в этом случае информация показывает. ЧТО имеет место команда выборки и необходимо чтение информации из памяти с использованием шины данных. При поступлении следующего синхросигнала (2) СК в модуле рабочих регистров получает единичное приращение содержимого и проверяется доступность ОЗУ- для выполнения цикла обращения к памяти. Кроме того, управляющий модуль опрашивает управляющую шину и при этом обновляется информация о состоянии системы. По очередному синхросигналу (3) команда считывается из ПЗУ через буфер на шину данных, с которой поступает на дешифратор. При появлении четвертого синхросигнала (4) содержимое рабочего регистра посылается в АЛУ, где оно складывается с содержимым аккумулятора. Очередным синхросигналом ЦПУ возвращается в исходное состояние (1). На этом выполнение команды сложения содержимого регистра и аккумулятора заканчивается. Цикл выполнения данной команды укладывается в один машинный цикл, содержащий четыре состояния. Сложение содержимого ячейки памяти с содержимым аккумулятора при использовании 8-разрядного адреса занимает два машинных цикла. Машинный цикл 1 аналогичен только что с(0[Ш;МДДНИЕ \осс  RlW MB Рис. 10.9. Пример машинного цикла 2 для случая сложения содержимого ячейки памяти и содержимого аккумулятора. рассмотренному машинному циклу с той разницей, что на четвертом такте синхронизации (4) выполнение операции в АЛУ блокируется. Граф переходов машинного цикла 2 показан на рис. 10.9. Стартовый синхроимпульс Фу вызывает переход в состояние Т1, а положительный фронт синхроимпульса 5*2 инициирует передачу адреса памяти на адресную шину. Эти же действия пока- Byqoep данных:  Uluna данных (3) Модуль дешифратора Унрадляющий (1) (Z)  Шина управления Рис. 10.10. Иллюстрация выполнения машинных циклов 2, 3 и 4 с помощью' обобщенной структурной схемы. заны на структурной схеме рис. 10.10. Значком (1) обозначено перемешение информации из модуля рабочих регистров на адресную шину. Следующий сигнал Ф\ вызывает переход в состояние Т2; на рис. 10.9 и 10.10 этот переход обозначен значком (2). Опрашивается состояние управляющей шины (STATUS СВ), и при появлении, синхросигнала Ф2 управляющий модуль разрешает использование шины данных (DBA) для пересылки информации. При поступлении очередного синхросигнала Фх и при условии, что память готова к обращению и не была получена команда останова, выполняется переход (3) в состояние ТЗ, в котором выдаются сигналы ЗАПИСЬ/ЧТЕНИЕ и сложения (ADD). Для осуществления этого сложения данные направляются в АЛУ и прибавляются к содержимому аккумулятора. Передний .фронт синхросигнала Ф2 переводит сигнал доступности шины на яизкий уровень (DBA). Таким образом, в машинном цикле 1 происходит одно чтение информации из ПЗУ, а в машинном цикле 2 - одно чтение из ПЗУ и одно чтение из ОЗУ. На этом выполнение операции сложения содержимого ячейки памяти с содержимым аккумулятора заканчивается, и при поступлении очередного синхросигнала Ф-[ происходит переход в состояние Т1. Выполнение команды складывается из машинного цикла 1 с четырьмя состояниями и машинного цикла 2 с тремя состояниями, т. е. всего имеют место два машинных цикла и семь состояний. Примером команды, занимающей три машинных цикла, является загрузка аккумулятора через систему ввода-вывода. Три цикла необходимы, если для адресации ввода-вывода использу- ется 16-разрядный адрес. Машинный цикл 1 выглядит, как показано на рис. 10.8. В состоянии Т1 (1) содержимое счетчика команд подается на адресную шину. В состоянии Т2 (2) выясняется состояние системы и содержимое счетчика команд увеличивается на 1. В состоянии ТЗ (3) из ПЗУ через буфер данных на модуль дешифратора подается команда. В состоянии Т4 (4) в модуль АЛУ осуществляется фиктивная загрузка. Рассмотрим машинные циклы 2 и 3, пользуясь рис. 10.10. При выполнении цикла 2 первый байт адреса подается на адресную шину в течение состояния Т1 (1). В состоянии Т2 (2) содержимое счетчика команд получает единичное приращение и выясняется состояние. В состоянии ТЗ (3) адрес порта ввода-вывода загружается в модуль рабочих регистров. Машинный цикл 3 завершает выполнение команды. В течение Т1(1) из модуля рабочих регистров на адресную шину подается второй байт адреса. В состоянии Т2 (2) выясняется состояние системы и разрешается использование шины данных. В качестве действия (3) производится передача данных из порта ввода-вывода в аккумулятор АЛУ. В каждом из машинных циклов 1 и 2 выполняется одно чтение информации из ПЗУ. В машинном цикле 3 имеет место одно чтение из ПЗУ и одно из порта ввода-вывода. Для выполнения данной команды требуются три машинных цикла, содержащих в общей сложности 10 состояний. Можно заметить, что число машинных циклов зависит от способа адресации. Для выполнения команды типа регистр - регистр необходим всего один машинный цикл. Выполнение команды, содержащей однобайтовый адрес, занимает два машинных цикла. Для реализации команды с двухбайтовым аДч ресом требуются три или большее число машинных циклов. Эф- фективность команды, содержащей двухбайтовый адрес, как правило, превышает эффективность команды с однобайтовым адресом более чем в два раза и поэтому ее выполнение часто занимает свыше трех машинных циклов. Пользователь имеет возможность организовать адресацию устройств ввода-вывода и памяти с помощью одно- или двухбайтных адресов и тем самым сбалансировать скорость выполнения и эффективность команд. Выше были описаны наиболее общие принципы построения схем, используемые большинством изготовителей микропроцессорных средств. Некоторые изготовители прибегают к различным усовершенствованиям рассмотренных конструктивных решений. Так, в одном из вариантов предполагается использование лишь одного синхроимпульса в каждом машинном цикле. При этом частота тактирования уменьшается примерно в три раза, а переходы между состояниями в пределах машинного цикла совершаются под действием внешних сигналов. Дальнейшая доработка связана с совершенствованием доступа к памяти. При этом несколько изменяется функционирование устройств и их программирование. Дальнейшее усовершенствование состоит в полном исключении синхросигнала Ф^. 10.4. ВВОД И ВЫВОД ИНФОРМАЦИИ Система ввода-вывода необходима для обмена информацией с внешними по отношению к микропроцессору устройствами. Ввод и вывод очень важны, если устройство должно выполнять какую-то полезную функцию. Микропроцессор, который не способен принимать и (или) передавать информацию, практически бесполезен. Интерфейс микро-ЭВМ по существу представляет собой буфер или регистр, служащий для связи ЦПУ микро-ЭВМ с каким-либо периферийным устройством. Для вывода информации из ЭВМ интерфейсный регистр хранит данные до тех пор, пока периферийное устройство не будет готово принять их. В ожидании этого ЦПУ может выполнять другие виды работы до тех пор, когда наступит сигнал от периферийного устройства. Аналогично при вводе информации интерфейсный регистр хранит данные, предназначенные для ЦПУ, в результате чего ЦПУ может обращаться к ним по мере необходимости. Основной задачей интерфейса является увязка во времени действий, выполняемых ЦПУ и периферийными устройствами. Изготовители микро-ЭВМУоставляют на рынок интерфейсные адаптеры, предназначеннке для упрощения сопряжения устройств микро-ЭВМ. Двумя наиболее широко применяемыми устройствами этого типа являются параллельный интерфейсный адаптер, предназначенный для осуществления быстрых пересылок информации, и последовательный интерфейсный адаптер, используемый при передаче информации на большие расстояния. На рис. 10.11 представлена блок-схема порта ввода-вывода микропроцессорной системы. Такой порт должен быть подсоединен к шине данных для пересылки данных и к адресной шине с целью его идентификации. В простейшем случае микропроцессор подает на устройство вывода по управляющей шине три сигнала. Синхросигнал Ф служит для синхронизации устройства Шана ваннысс Порт (интерфейс) бЫа-Мода ПРЕРЫВАНИЯ РАЗРЕШЕНИЕ Шина управления Адресная шина Рис. 10.11. Блок-схема порта ввода-вывода микропроцессорной системы. С Другими блоками микропроцессорной системы. Сигнал ЧТЕНИЕ/ЗАПИСЬ предназначен для указания направления пересылки данных. Сигнал РАЗРЕШЕНИЕ управляет поступлением информации на шину данных. Порт ввода-вывода запрашивает у микропроцессора выполнения действий по пересылке данных с помощью сигнала запроса прерывания (IRQ). На рис. 10.12 представлена блок-схема устройства управления типичного порта ввода-вывода. Синхронизация его работы с работой ЦПУ осуществляется путем обмена сигналами ЗАПРОС ПРЕРЫВАНИЯ и РАЗРЕШЕНИЕ. В то же время действия модуля ввода-вывода и периферийного устройства синхронизируются посредством сигналов ЗАПРОС и ОТВЕТ. Запрос на получение данных (РАЗРЕШЕНИЕ) передается от ЦПУ к периферийному устройству по линии ЗАПРОС. Если периферийное устройство готово к выполнению соответствующих действий, оно посылает по линии ОТВЕТ сигнал, который передается в ЦПУ по линии запроса прерывания. Конечно, в действительности модуль ввода-вывода имеет гораздо более сложную структуру, чем описано здесь. Основная трудность, встречающаяся при построении таких модулей, заключается в необходимости ограничения числа внешних выводов. Более эффективное их использование достигается за счет мультиплексирования информации внутри модуля. При этом увеличивается количество периферийных устройств, которые могут быть обслужены одним модулем ввода-вывода. На ранних этапах развития микро-ЭВМ считалось важным обеспечить управление вводом-выводом непосредственно от цпь ЧТЕНИЕ/ЗАПИСЬ РАЗРЕШЕНИЕ. упраЁления neputps-ОТВЕТ ycmpoucmSa ЗАПРОС ПРЕРЫВАНИЯ Рис. 10.12. Управляющие сигналы ввода-вывода. ЦПУ. При этом гибкость системы ввода-вывода несколько больше, но на ЦПУ ложится определенная нагрузка. Структура современного типового ЦПУ не ориентирована на осуществление ввода-вывода, основная нагрузка по решению этой задачи возлагается на интерфейсные адаптеры. Эти адаптеры делаются программируемыми, и, хотя ЦПУ по-прежнему может непосредственно управлять вводом-выводом, оно в значительной степени освобождено от действий, связанных с управлением. Это позволяет использовать ЦПУ более эффективно. Отметим также еще две особенности интерфейсов, которые необходимо принимать во внимание: 1. Направление передачи данных определяется программным путем. 2. Действия и направление передачи управляющих сигналов также задаются программой. Назначение и работа устройств ввода-вывода и интерфейсных адаптеров рассмотрены более конкретно в гл. 12. Что касается остальных разделов данной главы, то их задача состоит в том, чтобы подготовить чтсателя к рассмотрению конкретных и подробных описаний, составляющих гл. 12, а также материалов всех остальных глав книги. 10.5. РЕАЛЬНЫЕ МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ До сих пор наше рассмотрение носило обобщенный характер. В предыдущих главах были описаны стандартные компоненты, причем предполагалось, что они выпускаются в одном и том же виде всеми изготовителями. В действительности, однако, такой картины не наблюдается. Реальные компоненты микро-ЭВМ представляют собой функционально законченные схемы, специфичные для каждой фирмы-изготовителя. Более того, конструктивные и технологические особенности этих схем могут составлять собственность фирмы. Таким образом, приходится изучать конкретные микропроцессорные средства, выпускаемые различными фирмами [30-34]. В этой книге рассмотрены общие принципы функционирования микропроцессорных комплектов МС6800 фирмы Motorola и Intel 8085А фирмы Intel. Для удобства чтения информация, относящаяся к каждой из этих фирм, выделена специальными символами-разделителями □. Читателю, который хочет ознакомиться с семейством МС6800, следует обратиться к тем фрагментам текста, которые заключены между белыми квадратиками, как это имеет место в данном случае □. 0 Тем, кто хочет изучить семейство Intel 8085А, следует читать фрагменты, которые ограничены черными квадратиками, подобными тем, в которые заключен данный абзац. Й В данной книге рассматривается несколько ЦПУ, выпускаемых в рамках семейства Motorola МС6800. ЦПУ фирмы Motorola М.С6802, МС68А00 и МС68В00 имеют системы команд, совместимые с МС6800. Кроме того, в книге описывается ЦПУ Intel 8085А и совместимые с ним по системам команд ЦПУ Intel 8048 и 8080А. В семействе МС6800 используется цикл синхронизации, равный машинному циклу, а период синхронизации компонентов семейства Intel составляет примерно одну треть от длительности машинного цикла. Во избежание недоразумений под термином цикл , употребленным без уточняющих определений, будет пониматься машинный цикл. □ 10.5.1. ЦПУМС6800 Структурная схема ЦПУ МС6800 представлена на рис. 10.13. В системе МС6800 имеются 16-разрядная адресная шина и 8-разрядная шина данных. В состав ЦПУ входг стандартный модуль дешифратора. АЛУ включает в себя два 8-разрядных регистра-аккумулятора А и В и регистр состояния СС. К рабочим регистрам относятся индексный регистр (IX или X),. счетчик команд (СК) и указатель стека (УС). Все эти регистры 16-разрядные и служат для целей адресации. Блок управления ЦПУ имеет два входных синхросигнала 5*i и Ф2. Питание ЦПУ осуществляется по двум шинам Земля и -f 5 В . Кроме названных выше на ЦПУ поступает шесть следующих входных сигналов: 8-разрядная шина данных Регистр состояния тор А Аккумулятор В АЛИ Дешифратор Указатель стека Индексный регистр Счетчик команд Рабочие регистры Буфер

1Б-разрядная адресная шина Рис. 10.13. Структурная схема ЦПУ микропроцессора МС6800. 1. Запрос прерывания (IRQ). Служит для того, чтобы аппаратура ввода-вывода могла запрашивать у ЦПУ обслуживания прерываний. Прием процессором этих, запросов можно заблокировать программными средствами 2. Немаскируемое прерывание (NMl). Этот сигнал аналогичен IRQ с той разницей, что iNMI нельзя заблокировать с помощью программируемой маски прерываний. 3. Разрешение использования шины данных (DBE). Это управляющий сит'нал с тремя состояниями для шины данных ЦПУ. Обычно он формируется из синхросигнала Ф2 и предназначен для предотвращения таких ситуаций, когда выходные данные ЦПУ и памяти одновременно поступают на шину данных системы. 4. Трехстабильный управляющий сигнал (TSC). Служит для управления использованием адресной шины с таким расчетом, чтобы туда не поступала одновременно выходная ин- формация от двух устройств. Он необходим, когда к адресной шине подсоединены выходы ЦПУ и каких-либо других устройств. 5. Останов (HALT). Служит для останова ЦПУ, приводя адресную шину и шину данных в состояние высокого выходного импеданса, т. е. отключая их от внешних шин. 6. Сброс (RESET). Служит для приведения ЦПУ в исходное состояние перед началом выполнения программы. ЦПУ имеет три следующих выходных управляющих сигнала: 16-разрядная адресная шина (А0-А15) Деши(рратор АЭ-А15 Е АО-М ОЗУ Дешифратор А10-А15 са <м Со ti А0-А9 B0-JD7 ПЗУ 8-разрядная шина данных Шина управления Рис. 10.14. Типовое подключение ОЗУ и ПЗУ фирмы Motorola. 1. Чтение!Запись (RfW). Указывает, в каком режиме находится ЦПУ: чтения или записи: Это тоже трехстабильный сигнал, приводимый в состояние высокого импеданса под действием входных сигналов TSC и HALT. 2. Допустимое обращение к памяти (VMA). Служит для информирования памяти и портов ввода-вывода о том, что ЦПУ выполняет в данном цикле операцию чтения/записи. Этот сигнал должен подаваться на вход выборки кристалла РАЗРЕШЕНИЕ (ENABLE) с целью запрещения пересылки при VMA=0. 3. Шина доступна (ВА). Если ЦПУ по какой-то причине остановлен (сигналом HALT или в соответствии с выполняемой командой), данный сигнал сообщает другим устройствам о том, что шина свободна. 1 ... 19 20 21 22 23 24 25 ... 39 |

|||||||||

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |