|

|

|

|

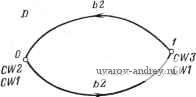

Главная страница » Электрика в театре » Мультиплексоры демультиплексоры в последовательностных схемах 1 ... 13 14 15 16 17 18 19 ... 39 функции для сигналов линий загрузки имеют вид fi!i = B, Ь1=Л, Ci = A Эти значения поступают в счетчик по линиям загрузки. На рис. 7.9 показана полная схема обобщенного интерфейса ввода. Неакти- о- 0-0- Вшадмини- Разрешение Выходной Яемульщи- ffig плексор щ Щ Загрузка 71зу-полон/паст 712\-ЦИКЛ \-НЕАКТИВЕН ВНИМАНИЕ Полностью < синхронный счетчик 709 Мульти-I плексор обратной сдязи ТактоВые имгуильсы Разрешение Цикл заВершен - f- АктиВен- Пуск* Прерывание Номер функции

а b с а b с Рис. 7.9. Схема обобщенного интерфейса на СИС-компонентах. реализованная на СИС-компонентах. Обратные связи с выхода счетчика ABC на задающие линии мультиплексоров приращения и обратной связи на схеме не показаны, но они опять подразумеваются и должны быть осуществлены при реализации схемы. 7.4. СХЕМЫ С ОДНИМ ВЫХОДОМ В гл. 6 было отмечено, что последовательностные схемы бывают двух типов: с одним выходом и несколькими входами. Подобная классификация может быть сделана и применительно к выходам схем. Общий подход, в соответствии с которым каждому состоянию сопоставляется отдельный выходной сиг- Рис. 7.10. Последовательност-ная схема с одним выходом на СИС-компонентах.

abed Последодательный Выход Двоично-десятичный < счвтчин 7f5 ТантоВые импульсы Разрешение нал, уже был описан. Однако широкое применение находят и такие последовательностные схемы, в которых каждому состоянию соответствует определенный уровень единственного выходного сигнала схемы. Одним из ярких примеров такого решения является передача данных, осуществляемая последовательно из соображений протяженности канала связи и (или) в соответствии с требованиями стандарта на способ кодирования сигналов. На рис. 7.10 показана схема преобразования параллельной формы представления данных в последовательную, реализованная на СИС-компонентах. В качестве примера рассмотрим передачу буквы К в коде ASCII) по асинхронной линии связи. Наиболее широко приме- ASCII (American Standard Code for Information Interchange-Американский стандартный код для обмена информацией). -Яргш. перее. няемый формат сигнала связи по асинхронной линии показан на рис. 7.11. Так как данный формат предназначен для асинхронной передачи, для обозначения начала и конца передаваемого символа используются один стартовый и два стоповых бита. Эти биты носят такие названия, потому что часто стартовый бит служит для запуска тактового генератора приемника, а стоповые биты - для его остановки. Убит данньиг 2cmono6bia: Si/mct -т I I СтартоВый бит -1---Г Полный цикл передачи симВола Рис.У.И. Формат символа при асинхронной передаче данных. В терминах цифровой связи стартовый бит, имеющий уровень логического нуля, называется пробелом. Стоповые биты, имеющие уровень логической единицы, называются посылками. Так как при передаче символов с помощью телетайпа рли дисплея оператором между отдельными символами обязательно имеют место паузы, они заполняются посылками. Шестнадцатеричный эквивалент (4В) семиразрядного кода буквы К приведен в табл. Б.З приложения Б. С учетом стартового и стоповых битов 4В передается в виде двоичной последо- 0000 0001 0010 0011 \ Разрешение 1001 1 1000 0111 -о- 0110 оюо -9 111 1 Рис. 7.12. Граф переходов схемы в процессе передачи символа. 0101 > о вательности 010010111. Граф переходов схемы, предназначенной для генерации буквы К в данном формате и выполненной на основе двоично-десятичного счетчика, приведен на рис. 7.12. Внешние связи выходного мультиплексора показаны на рис. 7.10. Они строятся в соответствии с графом переходов пу- = [SM\. Матрица входных сигналов [5] формируется следующим образом. Для столбца О, т. е. ABCD = 0000, необходимым выходным сигналом является 0; следовательно , So = 0. Для столбца 1 (y4BCD = 0001) требуется выходной сигнал 1, т. е. Si = l. Для столбца 2 {ABCD=0010) необходим выходной сигнал 0; следовательно, S2 = 0. Аналогичным образом получаем

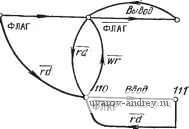

В данном случае значения входных сигналов So, 58 и Sg фиксированы. Передача других символов достигается за счет изменения значений входных сигналов Si-Sj. Как показано в разд. 7.1, характеристики счетчиков могут быть без труда модифицированы. При этом легко изменяется длительность цикла. 7.5. ПРОЕКТИРОВАНИЕ ГИБКИХ ТАКТИРУЕМЫХ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ Метод проектирования, изложенный в данной главе, позволяет строить'любые схемы на основе стандартной конфигурации компонентов. В гл. 6 было введено понятие программируемости схем с целью повышения их гибкости. С практической точки зрения создается впечатление, что при использовании понятия программируемости максимально эффективная последователь-постная схема может быть спроектирована так, что разместится на одной печатной плате. Данный подход часто используется в той или иной форме. Однако достигаемая при этом эффективность имеет своим следствием другую проблему, которую нельзя разрешить, но можно обойти. Она заключается в том, что проектируемая схема вырабатывает или требует большое число различных данных и информационных сигналов, и поэтому из-за роста числа внешних соединений приходится увеличивать размеры платы. Идея мультиплексирования данных во времени, рассмотренная в разд. 7.4, позволяет уменьшить число внешних связей. тем реализации следующего уравнения: а В интерфейсах микро-ЭВМ широко используются следующие принципы. На рис. 7.13 показан граф переходов схемы, предназначенной для записи информации, содержащейся в двух или более управляющих словах, в регистр памяти интерфейса с мультиплексированием во времени. Схема обычно находится в состоянии ожидания {АБС=000). При поступлении входного сигнала Чтение происходит переход в ЛВС=001. В этом состоянии содержимое регистра читается через интерфейс. Следующим тактовым импульсом схема воз-  fQOf ЧТЕНИЕ CIV3 100 о т о SllWO Рис. 7.13. Временное мультиплексирование информации. вращается в состояние ожидания. По входному сигналу Запись происходит переход в состояние АВС=0\0. В этом состоянии содержимое ЗАПИСИ передается в регистр С14 интерфейса. Последовательностная схема интерфейса проверяет значение бита Z)5 регистра С14. Если бит Z)5=0, то при поступлении очередного тактового импульса происходит переход в состояние АВС = 000. Если же £>5=1, то при поступлении входного сигнала Запись происходит либо переход в ЛВС=011, когда 5 = 0 (s=Z)lZ)0), либо переход в ЛВС=110, когда s=l. В этом состоянии содержимое ЗАПИСИ передается в регистр CW\ интерфейса. При поступлении последующих входных сигналов Запись происходит загрузка регистров интерфейса CW1 (при АВС= = 111) и CWЪ (в состоянии ЛВС=011). Обратите внимание на особенность данной схемы. Содержимое С14 может быть изменено в любой момент. Если s=l, то возможен доступ к регистрам CW\, CWI и CWЪ. Если s=0, то в регистры загружаются только два управляющих слова CW3 и CW4. Бит Z)5 называется битом внутреннего сброса. Описанный метод дает возможность использовать один набор линий для загрузки двух или более регистров. Существует другой способ, в соответствии с которым для загрузки трех регистров используются два набора линий. Граф переходов схемы  Рис. 7.14. Временное мультиплексирование два из трех . Если имеется возможность использовать два набора линий, то требуемый граф переходов значительно упрощается. Однако соответствующая схема интерфейса труднее для понимания с точки зрения программирования. В состоянии Z)=0 в регистры CWI и CW2 информация может быть послана по двум наборам линий. Если в регистре CWI бит 62=1, происходит переход в состояние D=l. При этом состоянии схемы. информация может быть послана в регистры CWI и CW3 по двум наборам линий. 7.6. УПРАЖНЕНИЯ У.7.1. Граф переходов, показанный на рис. У.7.1, служит для выработки следующей информационной последовательности: 1. Стартовый бит. Переход от высокого уровня к низкому используется для генерации на выходе стартового сигнала. 2. Биты символов. Схема допускает выбор количества генерируемых символов. Комбинация D3D2 заставляет схему генеривать пять символов, при £)3D2 вырабатывается шесть символов, при D3D2 - семь{ а при D3D2 - восемь. 3. П£изнак четности вырабатывается при наличии D4 и не вырабатывается при D4. Еще одна особенность данной схемы, которую мы здесь не рассматриваем, заключается в том, что при наличии D5 генерируется признак нечетности. 4. При наличии D7 генерируются два стоповых бита, а при D7 - только один. Разработайте схему, соответствующую заданному графу переходов. У.7.2. Программа обмена с квитированием для последовательного интерфейса может быть описана в аппаратных терминах с использованием графа перехода, показанного на рис. У.7.2. Пребывая в состоянии ОЖИДАНИЕ C£F= 00), интерфейс получает сигнал Массив данных готов {dsr) от периферийного устройства. При этом происходит переход в состояние EF=Ol, в котором выдается выходной ответный сигнал ТЕРМИНАЛ ДАННЫХ ГОТОВ (DTR). Проверяется содержимое управляющего регистра интерфейса. Если D0=1, то разрешается передача и происходит переход в состояние £F=10. В периферийное устройство посылается выходной сигнал запроса на передачу (RTS). Оно отвечает входным сигналом Готовность к передаче {cts), который вызывает переход схемы ин- Временного мультиплексирования два из трех приведен на рис. 7.14.  Г'ис. У.7.1. Генератор символов. EF 00 О- 0 ДАНИЕ £0 <? ТЕРМИНАЛ готов Ю ЗАПРОС НА Рис. У.7.2. Запуск последовательного ин-ПЕ РЕ ДАЧУ терфейса.- терфейса в состояние EF=\\. Выходной сигнал РАБОТА {RUN) выдается до тех пор, пока не будет получен входной сигнал Запрет (DO). Разработайте такую схему. У.7.3. Управление процедурой обмена с квитированием при использовании интерфейса для последовательной передачи данных часто осуществляется программно. В качестве примера на рис. У.7.3 приведен граф переходов схемы прерывания микро-ЭВМ. GfiJ ООО рлботд 001 т- О10  Рис. У.7.3. Граф переходов при передаче. При получении сигнала РАБОТА, генерируемого согласно граЛу перехо-дов( рис. У.7.2), происходит переход из состояния ОЖИДАНИЕ (ОЯ/=000) в состояние ОЯ/=001, при котором в микро-ЭВМ посылается сигнал ФЛАГ. Микро-ЭВМ проверяет значения бит DO и D2 интерфейса. Если бит D0=1, это интерпретируется как разрешение на передачу (ПЕРЕДАЧАХ РАЗРЕШЕНИЕ), и микро-ЭВМ отвечает выдачей данных и команды Запись. Происходит переход в состояние ОЯ/=0П. Флаг сбрасывается. После передачи данных входной сигнал Вывод переводит схему в состояние CHI=Oll. Снова выдается ФЛАГ, и микро-ЭВМ опять проверяет значение бита DO. Интерфейс осуществляет передачу данных, циклически проходя через состояния СЯ/=010 и ОН. Если микро-ЭВМ обнаруживает, что бит D2=l, это интерпретируется как разрешение на прием (ПРИЕМХРАЗРЕШЕНИЕ), и подается входной сигнал Чтение, вызывающий переход в состояние GHJ= 110. Флаг сбрасывается. При получении данных на вход Ввод происходит переход в состояние 0Я/=111. Проверяется значение бита D2, и, если D2=l, микро-ЭВМ вырабатывает входной сигнал Чтение. Данные принимаются, и интерфейс циклически проходит через состояния GHJ=\\Q и 111. Интерфейс приходит в исходное состояние, когда бит управляющего регистра D6=l. Разработайте описанную схему-. У.7.4. В одной из серийно выпускаемых мини-ЭВМ для инициирования работы интерфейса прямого доступа к памяти используются три 16-разрядных слова. Граф соответствующих переходов при обращении к управляюще- otaf  stcl запуск устройства Рис. У.7.4. Пересылка с прямым доступом к памяти (ПДП).- му регистру изображен на рис. У.7.4. Управляющее слово CWI содержит адрес периферийного устройства, CW2 - адрес первой ячейки памяти, а CW3 - необходимое количество передаваемых слов. По входному сигналу otal происходит переход в состояние XFZ=001. при котором в интерфейс посылается управляющее слово CWI. Аналогично сигнал Ыа2 вызывает переход в состояние XYZ=010 и затем в ОН, при которых в управляющий регистр интерфейса загружаются CW2 и CW3. Команда начала ввода stcl вызывает переход в состояние XYZ= 100, в котором на периферийное устройство подается выходной сигнал ЗАПУСК УСТРОЙСТВА. По команде sifc2 происходит переход в состояние XYZ=lOl, при котором начинается пересылка с прямым доступом к памяти. Разработайте данную схему. ГЛАВА 8 ПОСТРОЕНИЕ ГРАФА ПЕРЕХОДОВ В предыдущих главах читателю предлагалось разрабатывать схемы, используя имеющиеся графы переходов. Последующие этапы этой разработки являются чрезвычайно важными. Необходимо, однако, понимать, что основу процесса проектирования составляют графы переходов, построение которых осуществляется путем преобразования словесного описания задачи в ее графическое описание. При этом подразумевается выполнение ряда условий. Первое из них предполагает наличие словесного описания задачи. На самом деле так оказывается далеко не всегда. Перед разработчиком часто ставят задачу не только построения графа переходов проектируемой схемы, но и словесного описания решаемой задачи. На практике проблема вырисовывается в ходе обсуждения, после которого разработчик излагает ее на бумаге. За первой попыткой фомулировки задачи следует новое обсуждение. Наиболее содержательный комментарий, на который может при этом рассчитывать разработчик, звучит так: Я не знаю, как это должно работать, но таким образом это работать не должно . Б данной главе из практических соображений предполагается, что имеется словесная постановка задачи. Описываемые методы служат для преобразования словесной постановки в граф переходов. Этапы этого преобразования рассматриваются в нижеследующих разделах. 8.1. ФОРМАТ ПРЕДСТАВЛЕНИЯ ГРАФА ПЕРЕХОДОВ Как отмечалось выше, граф переходов служит для представления всех сведений о последовательностной схеме, подлежащей разработке. При этом требуется весьма осторожно обращаться с указанной информацией. Входные сигналы изображаются в виде направленных линий, входящих в кружки, служащие для представления состояния схемы. Стрелки указывают направление последовательности событий. Входные сигналы поступают от внешних источников. Чтобы стрелки четко различались, они изображаются в 1 ... 13 14 15 16 17 18 19 ... 39 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |